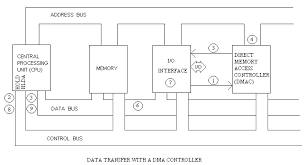

DATA TRANSFER WITH A DMA CONTROLLER

DATA TRANSFER WITH A DMA CONTROLLER

Penjelasan :

Selama transfer byte masukan blok, urutan berikut terjadi sebagai byte data yang dikirim dari

antarmuka ke memori:

1. Antarmuka mengirimkan DMA controller permintaan untuk layanan DMA.

2. Permintaan Bus dibuat ke pin HOLD (aktif Tinggi) pada mikroprosesor 8086 dan

pengendali mendapatkan kendali atas bus.

3. Hibah Bus dikembalikan ke pengontrol DMA dari pin Hold Acknowledge (HLDA)

(Aktif Tinggi) pada mikroprosesor 8086.

4. Pengontrol DMA menempatkan isi register alamat ke bus alamat.

5. Kontroler mengirimkan antarmuka pengakuan DMA, yang memberi tahu antarmuka untuk ditempatkan

data pada bus data. (Untuk output, ini menandakan antarmuka untuk mengunci data berikutnya yang ditempatkan pada

bis.)

6. Data byte ditransfer ke lokasi memori yang ditunjukkan oleh bus alamat.

7. Antarmuka mengaitkan data.

8. Permintaan Bus dijatuhkan, pin HOLD pergi Rendah, dan pengendali melepaskan bus.

9. Hibah Bus dari mikroprosesor 8086 dijatuhkan dan pin HLDA menjadi Rendah.

10. Register alamat bertambah 1.

11. Hitungan byte dikurangi dengan 1.

12. Jika jumlah byte tidak nol, kembalikan ke langkah 1, jika tidak hentikan

Opsi Direct Memory Access Controller (DMAC) untuk transfer data

DMA Controller memiliki beberapa opsi yang tersedia untuk transfer data. Mereka:

1) Cycle Steal:

Sinyal baca atau tulis dihasilkan oleh DMAC, dan perangkat I / O menghasilkan atau mengaitkandata. DMAC secara efektif mencuri siklus dari prosesor untuk mentransfer byte, jadi tunggal Transfer byte juga dikenal sebagai siklus mencuri.

2) Transfer Burst:

Untuk mencapai transfer blok, beberapa DMAC menggabungkan sekuensing otomatis dari nilai yang disajikan di bus alamat. Register digunakan sebagai jumlah byte, yang dikurangi untuk setiap transfer byte, dan pada hitungan byte mencapai nol, DMAC akan merilis bus. Ketika DMAC beroperasi dalam burst mode, CPU dihentikan selama durasi transfer data.

3) DMA Tersembunyi:

Dimungkinkan untuk melakukan DMA tersembunyi, yang transparan untuk operasi normal dari CPU. Di kata lain, bus diambil oleh DMAC ketika prosesor tidak menggunakannya. DMAC memonitor eksekusi prosesor, dan ketika ia mengenali prosesor yang mengeksekusi instruksi yang memiliki siklus jam kosong yang cukup untuk melakukan transfer byte, itu menunggu sampai prosesor decoding kode op, lalu ambil bus selama waktu ini. Prosesor tidak diperlambat, tetapi Terus memproses secara normal. Tentu, transfer data oleh DMAC harus diselesaikan sebelumnyaprosesor dimulai.

Komentar

Posting Komentar